Key Use Cases

Tools in Detail

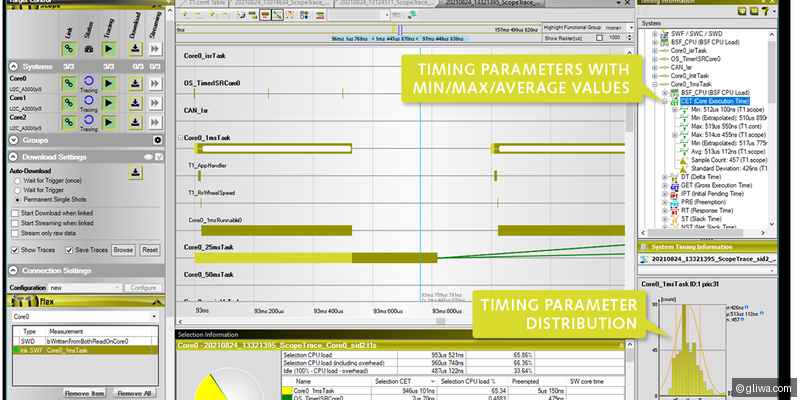

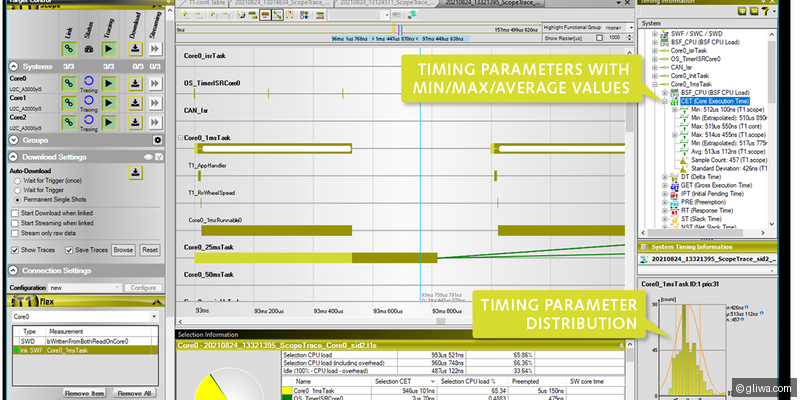

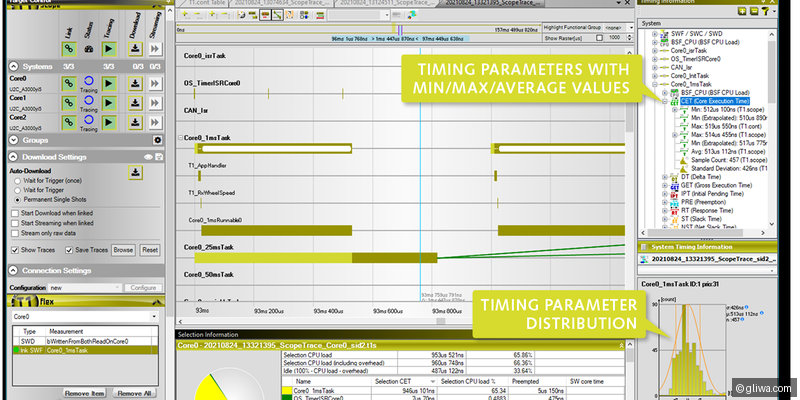

GLIWA T1

Industry-standard runtime monitor for AUTOSAR OS. Non-intrusive tracing of task/runnable execution, ISR timing, and resource usage. Provides visual timeline views and statistical analysis.

GLIWA T1.flex

Flexible extension of T1 for custom monitoring scenarios. Supports user-defined trace points and works without OS instrumentation hooks for legacy or non-AUTOSAR systems.

GLIWA T1.stack

Stack usage analyzer that measures actual worst-case stack consumption for tasks and ISRs. Critical for safe stack sizing in memory-constrained ECU projects.

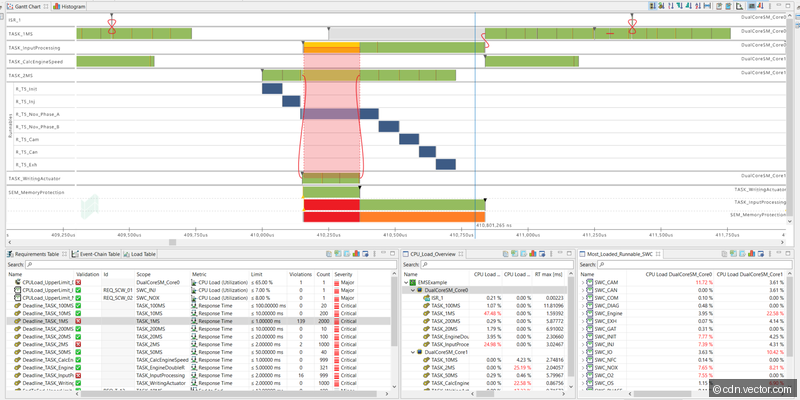

Timing Architects TA

System-level timing design and verification tool. Models end-to-end timing chains across ECUs, validates against AUTOSAR timing requirements, and supports TIMEX analysis.

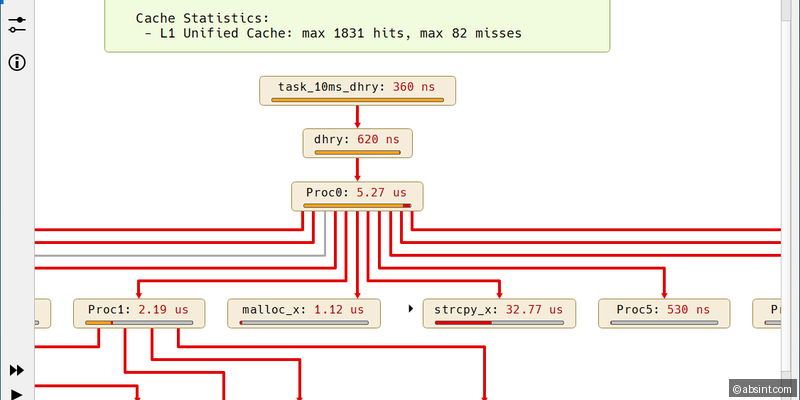

AbsInt aiT

Static WCET analysis tool providing mathematically proven upper bounds on execution time. Qualified for ISO 26262 and DO-178C, used for safety-critical timing certification.

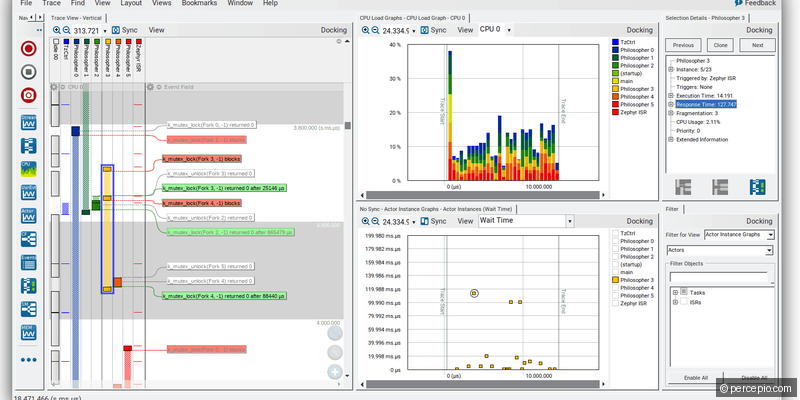

Percepio Tracealyzer

Visual trace analysis tool for RTOS-based systems. Displays task execution, synchronization, and communication patterns with timeline views. Supports FreeRTOS, Linux, and more.

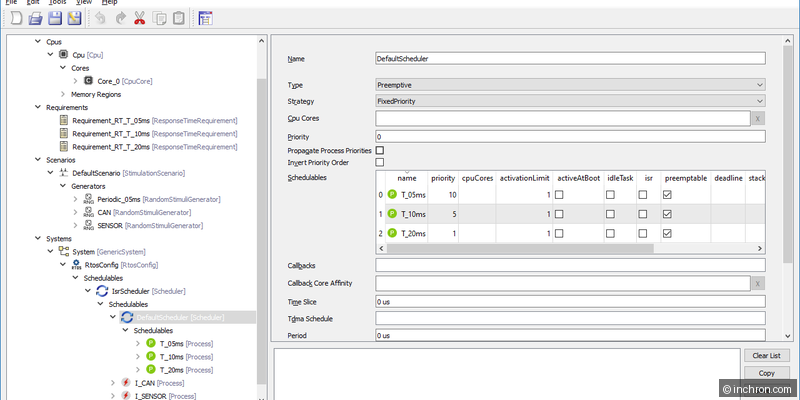

INCHRON chronSIM

Timing simulation tool for system-level performance prediction. Simulates multi-ECU timing behavior including network delays, task scheduling, and interrupt handling.

Industry Context

Timing failures are insidious - they may only manifest under specific, rare load conditions. A task occasionally overrunning its deadline by microseconds might work during development but fail catastrophically under full communication load. ISO 26262 explicitly requires timing evidence for safety-relevant functions. Multi-core MCUs (Infineon AURIX with up to 6 cores) introduce additional complexity through shared-resource contention, cache interference, and bus arbitration that can dramatically inflate execution times.

Typical Workflow

During architecture design, TA and chronSIM provide early timing feasibility. During implementation, GLIWA T1.flex profiles individual functions. During integration, GLIWA T1 monitors full AUTOSAR OS scheduling under realistic load. T1.stack verifies stack allocation. For certification, AbsInt aiT provides formal WCET bounds while measurement-based evidence from T1 complements with empirical validation. The combination provides the comprehensive evidence ISO 26262 assessors expect.

Selection Guide

Pro Tips

Measure timing under worst-case load - enable all communication, activate all diagnostics, and inject maximum DTC storage.

Leave 30%+ margin between measured WCET and deadline - execution times increase with compiler changes and multi-core interference.

Monitor stack usage continuously, not just once - consumption varies dramatically with different input paths.

For multi-core MCUs, measure safety-critical functions both in isolation and under full system load.

Document your timing analysis approach as part of the safety case - assessors need the methodology, not just results.